# UNIVERSIDAD DE LA LAGUNA

«El modelo de computación colectiva: una metodología eficiente para la ampliación del modelo de librería de paso de mensajes con paralelismo de datos anidado»

> Autor: Francisco de Sande González Director: Dr. D. Casiano Rodríguez León

> Departamento de Estadística, Investigación Operativa y Computación

Don Casiano Rodríguez León, Doctor en Matemáticas y Catedrático del Área de Lenguajes y Sistemas Informáticos adscrito al Departamento de Estadística, Investigación Operativa y Computación de la Universidad de La Laguna,

#### Certifica

Que la presente memoria titulada *El Modelo de Computación Colectiva: Una Metodología eficiente para la ampliación del Modelo de Librería de Paso de Mensajes con Paralelismo de Datos Anidado*, ha sido realizada bajo su dirección por el Licenciado D. Francisco de Sande González y constituye su Tesis para optar al grado de Doctor Ingeniero en Informática.

Y para que así conste, en cumplimiento de la legislación vigente y a los efectos que haya lugar, firma la presente en La Laguna, a cinco de octubre de mil novecientos noventa y ocho.

Fdo.: Casiano Rodríguez León

A mis padres, Rosa y Pompeyo, a quienes debo todo

A mis hermanas, Daine y Sole por su esfuerzo en mi educación

# **Agradecimientos**

Quisiera expresar mi agradecimiento en primer lugar al profesor D. Casiano Rodríguez León por haberme permitido integrarme en su grupo de investigación, por el entusiasmo que siempre me ha infundido y por su intensa dedicación a la realización de este trabajo.

A mis compañeros del Grupo de Paralelismo Coro, Félix, Paco, Jose Luis, Dani y Jesús Alberto por las enriquecedoras discusiones que hemos mantenido, por su ayuda desinteresada en tantas ocasiones y en particular en la revisión de esta memoria, por tantos ratos compartidos y en definitiva, por su amistad.

A los compañeros del Departamento de Estadística, I. O. y Computación y del Centro Superior de Informática por su apoyo.

A Instituciones como el C4, Ciemat, Instituto de Astrofísica de Canarias, Centro de Computación de Edimburgo y Centro Superior de Informática de la Universidad de La Laguna que nos han brindado la oportunidad de utilizar sus máquinas e instalaciones, imprescindibles en la realización de esta memoria.

Mi agradecimientos también para Oriol Riu, del Cepba, Ingrid Bárcenas, Montserrat Mestres y Joan Cambras del Cesca y Pablo López del Instituto de Astrofísica de Canarias, todos ellos administradores de las máquinas en que se han llevado a cabo los experimentos computacionales de este trabajo.

A Lola, por su comprensión, apoyo y cariño.

# ÍNDICE

| Capítulo I         PLATAFORMAS SOFTWARE Y HARDWARE       1         1.2. PLATAFORMAS SOFTWARE       2         1.2. 1. La máquina virtual paralela (PVM)       2         1.2. 1. 1. Principales características de PVM       4         1.2. 1. 2. Primitivas PVM       5         1.2. 2. Message Passing Interface (MPI)       8         1.2. 2. 1. La plataforma MPICH       9         1.2. 2. 2. Primitivas MPI       11         1.3. PLATAFORMAS HARDWARE       13         1.3. 1. Redes de área local       13         1.3. 1. Tipos de medio físico       13         1.3. 1. 2. Topologías       14         1.3. 1. 3. Modos de Acceso       14         1.3. 2. IBM SP2       15         1.3. 3. Silicon Graphics Origin 2000       16         1.3. 4. Digital Alpha Server 8400       18         1.3. 5. CRAY T3E       19         1.3. 6. CRAY T3D       21         1.3. 7. Hitachi SR2201       22         Capítulo II         El MODELO PRAM       25         2.1. I. Introducción       25         2.1. 1. Variantes según la resolución de los conflictos de acceso a memoria       25         2.1. 2. Factibilidad del modelo PRAM       26 | Prólogo                                     | . XVII |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|--------|

| Introducción                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Capítulo I                                  |        |

| 1.2. Plataformas Software       2         1.2.1. La máquina virtual paralela (PVM)       2         1.2.1. Principales características de PVM       4         1.2. Primitivas PVM       5         1.2. Message Passing Interface (MPI)       8         1.2. I. La plataforma MPICH       9         1.2. 2. Primitivas MPI       11         1.3. Plataformas Hardware       13         1.3. 1. Redes de área local       13         1.3. 1. Tipos de medio físico       13         1.3. 1. Z. Topologías       14         1.3. 1. 3. Modos de Acceso       14         1.3. 2. IBM SP2       15         1.3. 3. Silicon Graphics Origin 2000       16         1.3. 4. Digital Alpha Server 8400       18         1.3. 5. CRAY T3E       19         1.3. 7. Hitachi SR2201       21         1.3. 7. Hitachi SR2201       22         Capítulo II         El MODELO PRAM       25         2.1. I. Nariantes según la resolución de los conflictos de acceso a memoria       25         2.1. 2. Factibilidad del modelo PRAM       26                                                                                                                        | PLATAFORMAS SOFTWARE Y HARDWARE             | 1      |

| 1.2.1.La máquina virtual paralela (PVM)       2         1.2.1.1.Principales características de PVM       4         1.2.1.2.Primitivas PVM       5         1.2.2.Message Passing Interface (MPI)       8         1.2.2.1.La plataforma MPICH       9         1.2.2.2.Primitivas MPI       11         1.3.Plataformas Hardware       13         1.3.1.Redes de área local       13         1.3.1.1.Tipos de medio físico       13         1.3.1.2.Tōpologías       14         1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAYT3E       19         1.3.7.Hitachi SR2201       21         Capítulo II         El MODELO PRAM       25         2.1.Introducción       25         2.1.I.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                            | Introducción                                | 1      |

| 1.2.1.1.Principales características de PVM       4         1.2.1.2.Primitivas PVM       5         1.2.2.Message Passing Interface (MPI)       8         1.2.2.1.La plataforma MPICH       9         1.2.2.2.Primitivas MPI       11         1.3.Plataformas Hardware       13         1.3.1.Redes de área local       13         1.3.1.Tipos de medio físico       13         1.3.1.2.Topologías       14         1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAYT3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El MODELO PRAM       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                      |                                             |        |

| 1.2.1.1.Principales características de PVM       4         1.2.1.2.Primitivas PVM       5         1.2.2.Message Passing Interface (MPI)       8         1.2.2.1.La plataforma MPICH       9         1.2.2.2.Primitivas MPI       11         1.3.Plataformas Hardware       13         1.3.1.Redes de área local       13         1.3.1.Tipos de medio físico       13         1.3.1.2.Topologías       14         1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAYT3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El MODELO PRAM       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                      | 1.2.1.La máquina virtual paralela (PVM)     | 2      |

| 1.2.1.2.Primitivas PVM       5         1.2.2.Message Passing Interface (MPI)       8         1.2.2.1.La plataforma MPICH       9         1.2.2.2.Primitivas MPI       11         1.3.Plataformas Hardware       13         1.3.1.Redes de área local       13         1.3.1.Tipos de medio físico       13         1.3.1.Tipos de medio físico       13         1.3.1.Tipos de medio físico       13         1.3.1.Rodos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAYT3E       19         1.3.6.CRAYT3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El MODELO PRAM       25         2.1.Introducción       25         2.1.I.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                              | 1.2.1.1.Principales características de PVM  | 4      |

| 1.2.2.1.La plataforma MPICH       9         1.2.2.2.Primitivas MPI       11         1.3.Plataformas Hardware       13         1.3.1.Redes de área local       13         1.3.1.Tipos de medio físico       13         1.3.1.Z.Topologías       14         1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El MODELO PRAM       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                             |                                             |        |

| 1.2.2.1.La plataforma MPICH       9         1.2.2.2.Primitivas MPI       11         1.3.Plataformas Hardware       13         1.3.1.Redes de área local       13         1.3.1.Tipos de medio físico       13         1.3.1.Z.Topologías       14         1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El MODELO PRAM       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                             | 1.2.2.Message Passing Interface (MPI)       | 8      |

| 1.2.2.2.Primitivas MPI       11         1.3.Plataformas Hardware       13         1.3.1.Redes de área local       13         1.3.1.Tipos de medio físico       13         1.3.1.2.Topologías       14         1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAYT3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El modelo pram       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.2.2.1.La plataforma MPICH                 | 9      |

| 1.3. Plataformas Hardware       13         1.3. 1. Redes de área local       13         1.3. 1. 1. Tipos de medio físico       13         1.3. 1. 2. Topologías       14         1.3. 1. 3. Modos de Acceso       14         1.3. 2. IBM SP2       15         1.3. 3. Silicon Graphics Origin 2000       16         1.3. 4. Digital Alpha Server 8400       18         1.3. 5. CRAY T3E       19         1.3. 6. CRAY T3D       21         1.3. 7. Hitachi SR2201       22         Capítulo II         El modelo pram       25         2.1. Introducción       25         2.1. I. Variantes según la resolución de los conflictos de acceso a memoria       25         2.1. 2. Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1.2.2.2.Primitivas MPI                      | 11     |

| 1.3.1.1.Tipos de medio físico       13         1.3.1.2.Topologías       14         1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El modelo pram       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |        |

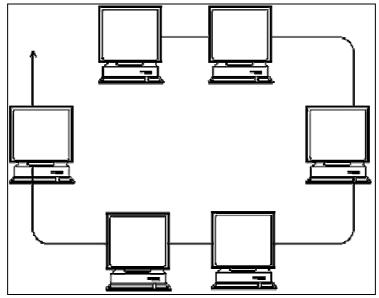

| 1.3.1.2.Topologías       14         1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El modelo Pram       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.3.1.Redes de área local                   | 13     |

| 1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El modelo pram       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.3.1.1.Tipos de medio físico               | 13     |

| 1.3.1.3.Modos de Acceso       14         1.3.2.IBM SP2       15         1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El modelo pram       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1.3.1.2. Topologías                         | 14     |

| 1.3.3.Silicon Graphics Origin 2000       16         1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El modelo pram       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                             |        |

| 1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         EL MODELO PRAM       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.3.2.IBM SP2                               | 15     |

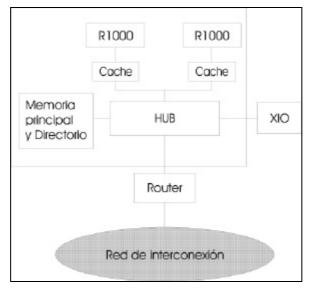

| 1.3.4.Digital Alpha Server 8400       18         1.3.5.CRAY T3E       19         1.3.6.CRAY T3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         EL MODELO PRAM       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1.3.3.Silicon Graphics Origin 2000          | 16     |

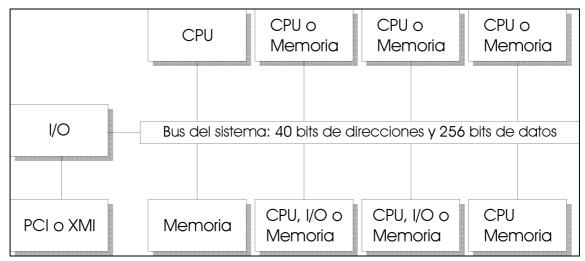

| 1.3.5.CRAYT3E       19         1.3.6.CRAYT3D       21         1.3.7.Hitachi SR2201       22         Capítulo II         El modelo pram       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |        |

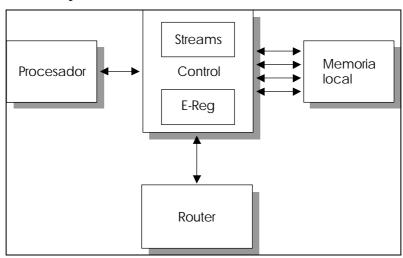

| 1.3.7.Hitachi SR2201       22         Capítulo II         EL MODELO PRAM       25         2.1.Introducción       25         2.1.1.Variantes según la resolución de los conflictos de acceso a memoria       25         2.1.2.Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |        |

| Capítulo IIEl MODELO PRAM252.1.Introducción252.1.1.Variantes según la resolución de los conflictos de acceso a memoria252.1.2.Factibilidad del modelo PRAM26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 1.3.6.CRAY T3D                              | 21     |

| EL MODELO PRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1.3.7.Hitachi SR2201                        | 22     |

| 2.1. Introducción       25         2.1.1. Variantes según la resolución de los conflictos de acceso a memoria 25         2.1.2. Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Capítulo II                                 |        |

| 2.1. Introducción       25         2.1.1. Variantes según la resolución de los conflictos de acceso a memoria 25         2.1.2. Factibilidad del modelo PRAM       26                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | EL MODELO PRAM                              | 25     |

| 2.1.1. Variantes según la resolución de los conflictos de acceso a memoria 25<br>2.1.2. Factibilidad del modelo PRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                             |        |

| 2.1.2.Factibilidad del modelo PRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                             |        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                             |        |

| 2 2 ACTIVACIÓN V ASIGNACIÓN DE PROCESADORES 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2.2.Activación y asignación de procesadores |        |

| 2.2.1.Ejemplo 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                             |        |

| 2.3.El lenguaje La Laguna (ll) 30                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | J 1                                         |        |

| 2.3.1.Implementaciones                                          | 33 |

|-----------------------------------------------------------------|----|

| 2.3.2.Ejemplos                                                  |    |

| 2.3.2.1.Suma de prefijos                                        |    |

| 2.3.2.2.Ordenación bitónica                                     | 38 |

| 2.3.2.3.Un Quicksort paralelo                                   |    |

| 2.4. TIEMPO Y NÚMERO DE PROCESADORES                            | 39 |

| 2.4.1.Suma de prefijos                                          | 39 |

| 2.4.2.Ordenación Bitónica                                       | 40 |

| 2.4.3. Quicksort Paralelo                                       | 40 |

| 2.5. Asignación de Procesadores Controlada por el Programador   | 41 |

| 2.6. Las Sentencias Condicionales como Sentencias de Asignación | DE |

| Procesadores                                                    | 42 |

| 2.7. Aceleraciones y paradojas                                  | 42 |

| 2.7.1.Límites en la Aceleración alcanzable                      | 43 |

| 2.7.2.Aceleración Superlineal                                   | 43 |

| 2.8.El Coste, La Eficiencia y el Trabajo                        | 45 |

| 2.8.1.Reduciendo el Número de Procesadores                      | 46 |

| 2.8.2.Teorema de Brent Generalizado                             | 47 |

| 2.8.3.La Ley de Amdahl Generalizada                             | 49 |

| 2.9. Simulación del Modelo PRAM por una Mariposa                | 50 |

| Capítulo III                                                    |    |

| FORK 95 Y LA SBPRAM                                             | 53 |

| 3.1.Introducción                                                | 53 |

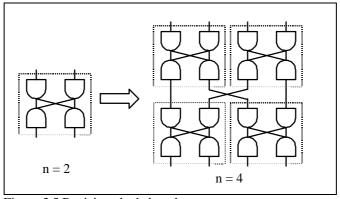

| 3.2.La SB-PRAM                                                  | 53 |

| 3.2.1.Los procesadores                                          | 55 |

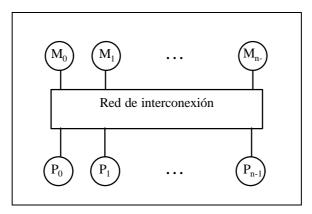

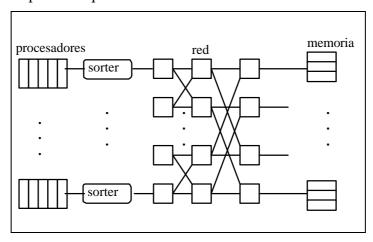

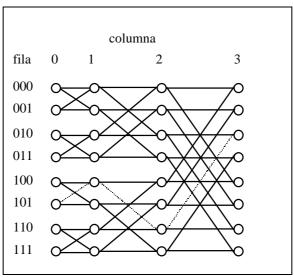

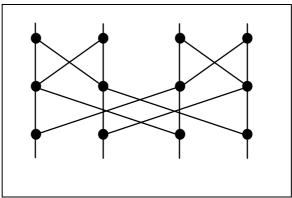

| 3.2.2.La red de interconexión                                   | 57 |

| 3.2.2.1.El algoritmo de ruteo                                   | 59 |

| 3.3.Fork95                                                      |    |

| 3.3.1.La ejecución de programas Fork95                          |    |

| 3.3.2. Variables privadas y compartidas                         |    |

| 3.3.3.Operaciones de prefijos                                   |    |

| 3.3.4.Zonas síncronas y asíncronas en los programas Fork95      | 67 |

| 3.3.5.El concepto de grupo en Fork95                            |    |

| 3.3.6. Ejecución síncrona y asíncrona. La sentencia join        | 72 |

| 3.3.7.Punteros y heaps                                                   | 75   |

|--------------------------------------------------------------------------|------|

| 3.3.8.Precauciones a la hora de programar en Fork95                      | 77   |

| 3.3.9.Algunos ejemplos                                                   | 78   |

| 3.3.9.1.La suma de prefijos                                              |      |

| 3.3.9.2.El Quicksort                                                     |      |

| 3.3.9.3.Otra implementación del Quicksort                                |      |

| 3.3.9.4.Mergesort                                                        |      |

| 3.3.9.5.La FFT                                                           |      |

| 3.3.9.6.La Quickhull                                                     |      |

| Capítulo IV                                                              |      |

| El modelo de Computación Colectiva                                       | 89   |

| 4.1.Introducción                                                         |      |

| 4.2.Generalidades                                                        |      |

| 4.3.Definiciones                                                         | . 92 |

| 4.4. Clasificación de problemas                                          |      |

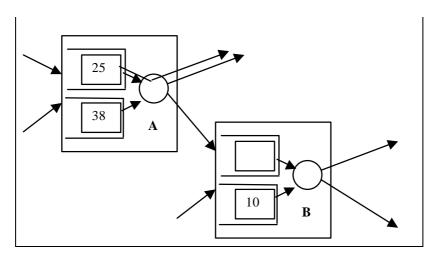

| 4.5. HIPERCUBOS DINÁMICOS                                                | 104  |

| 4.5.1. Hipercubo binario                                                 | 106  |

| 4.5.2.Hipercubo k-ario                                                   |      |

| 4.5.3. Hipercubo dinámico                                                |      |

| 4.6. Implementación de algoritmos divide y vencerás en Computaci         |      |

| COLECTIVA COMÚN (CCC) MEDIANTE HIPERCUBOS DINÁMICOS                      | 109  |

| 4.6.1.Ejemplos                                                           | 112  |

| 4.6.1.1.La transformada rápida de Fourier                                | 112  |

| 4.6.1.2. Cálculo de la envoltura convexa: Quickhull                      | 114  |

| 4.6.1.3. Optimizaciones en la utilización de la memoria en el cálculo de | e la |

| envoltura convexa                                                        |      |

| 4.6.1.4.Ordenación: Quicksort                                            | 117  |

| 4.6.1.5.Un algoritmo de búsqueda                                         |      |

| 4.6.2. Equilibrado de la carga en Computación Colectiva Común media      |      |

| Hipercubos Dinámicos Ponderados                                          |      |

| 4.7. Implementación de algoritmos divide y vencerás en computacion       |      |

| COLECTIVA (CC) MEDIANTE HIPERCUBOS DINÁMICOS                             | 121  |

| 4.7.1.El Quicksort Distribuido                                           |      |

| 4.7.2.Quickhull Distribuida                                              |      |

| 4.7.3. Equilibrado de la carga en Computación Colectiva          | 127  |

|------------------------------------------------------------------|------|

| 4.8. EL MODELO COLECTIVO COMO MODELO DE PREDICCIÓN DEL TIEMPO    | ) DE |

| CÓMPUTO                                                          | 130  |

| 4.8.1.Análisis del Quicksort de tipo Común-Común                 | 132  |

| 4.8.2.Análisis de la FFT                                         | 133  |

| 4.8.3. Análisis del algoritmo de ordenación por Muestreo Regular | 133  |

| 4.9.La Laguna C                                                  | 135  |

|                                                                  |      |

| Capítulo V                                                       |      |

| Otros Lenguajes y Herramientas                                   | 139  |

| 5.1.NESL                                                         |      |

| 5.1.1.Operaciones paralelas sobre secuencias                     |      |

| 5.1.2.Paralelismo anidado                                        |      |

| 5.1.3.Pares                                                      |      |

| 5. 1. 4. Tipos                                                   |      |

| 5.1.5.Definición del lenguaje                                    |      |

| 5.1.5.1.Datos                                                    |      |

| 5.1.5.1.1. Tipos de datos atómicos                               |      |

| 5.1.5.1.2.Secuencias ([])                                        |      |

| 5.1.5.1.3. Tipos registros (datatype)                            | 147  |

| 5.1.5.2. Funciones y constructos                                 |      |

| 5.1.5.2.1.Condicionales (if)                                     | 148  |

| 5.1.5.2.2. Asignación a variables locales (let)                  | 149  |

| 5.1.5.2.3.El constructor aplicar-a-cada-uno                      | 149  |

| 5.1.5.2.4. Definición de nuevas funciones (function)             | 151  |

| 5.1.5.2.5.Asignaciones globales                                  | 151  |

| 5.1.6.Ejemplos                                                   | 151  |

| 5.1.6.1.Búsqueda de una cadena en otra                           | 152  |

| 5.1.6.2. Cálculo de números primos                               | 153  |

| 5.1.6.3.El Quicksort                                             | 154  |

| 5.2.V                                                            |      |

| 5.2.1.Elementos de V                                             | 155  |

| 5.3.El aplanamiento del paralelismo                              |      |

| 5.4.Aperitif                                                     | 158  |

# Capítulo VI

| RESULTADOS COMPUTACIONALES                    | 165 |

|-----------------------------------------------|-----|

| 6.1. Introducción                             | 165 |

| 6.2.La Transformada rápida de Fourier         | 166 |

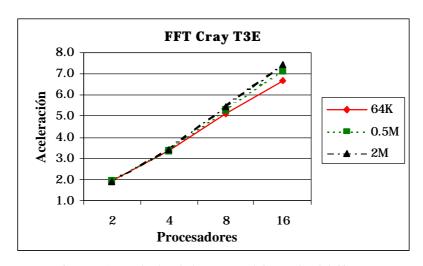

| 6.2.1.Cray T3E (Ciemat)                       | 167 |

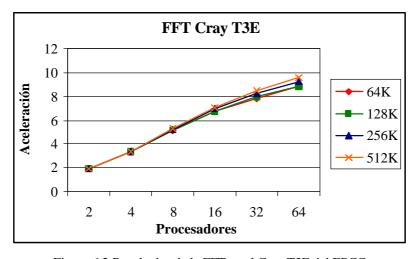

| 6.2.2.Cray T3E (EPCC)                         | 168 |

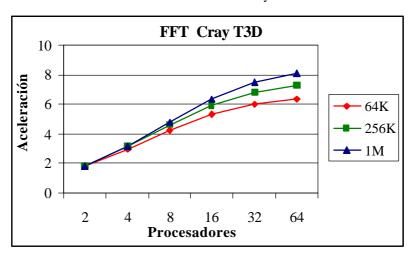

| 6.2.3.Cray T3D                                | 169 |

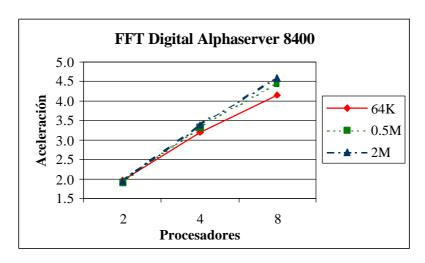

| 6.2.4.Digital Alphaserver 8400                | 170 |

| 6.2.5.Hitachi SR2201                          | 171 |

| 6.2.6.IBM SP2                                 | 172 |

| 6.2.7. Silicon Graphics Origin 2000 (karnak3) | 173 |

| 6.2.8. Silicon Graphics Origin 2000 (karnak2) |     |

| 6.3.EL QUICKSORT                              |     |

| 6.3.1.Cray T3E                                |     |

| 6.3.2.Cray T3D                                | 181 |

| 6.3.3.Digital Alphaserver 8400                | 184 |

| 6.3.4.IBM SP2                                 |     |

| 6.3.5.IBM SP2 (switch antiguo)                | 190 |

| 6.3.6.Silicon Graphics Origin 2000 (karnak3)  | 193 |

| 6.3.7.Silicon Graphics Origin 2000 (karnak2)  |     |

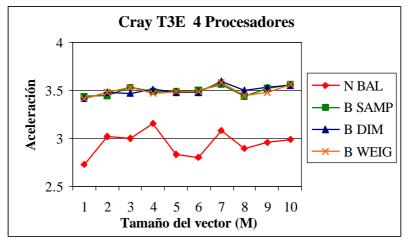

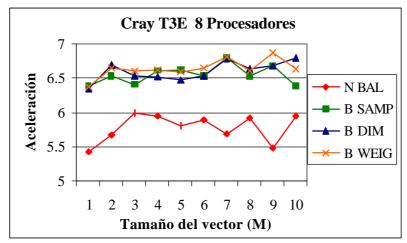

| 6.4.La Quickhull                              |     |

| 6.4.1.Cray T3E                                |     |

| 6.4.2.Cray T3D                                | 202 |

| 6.4.3.Digital Alphaserver 8400                | 203 |

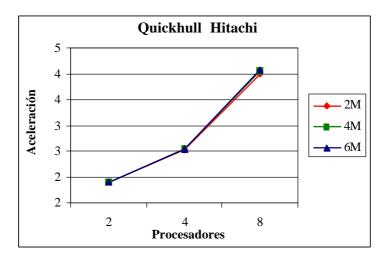

| 6.4.4.Hitachi SR2201                          |     |

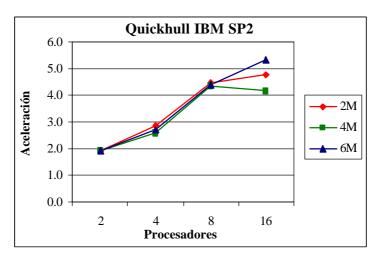

| 6.4.5.IBM SP2                                 |     |

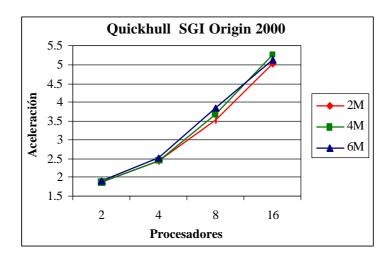

| 6.4.6. Silicon Graphics Origin 2000 (karnak3) | 206 |

| 6.5.EL QUICKSORT DISTRIBUIDO                  |     |

| 6.5.1.Cray T3E                                | 209 |

| 6.5.2.Digital Alphaserver 8400                |     |

| 6.5.3.IBM SP2                                 | 213 |

| 6.5.4. Silicon Graphics Origin 2000 (karnak3) | 215 |

| 6.6.EL ALGORITMO DE BÚSQUEDA                  |     |

| 6.6.1.Cray T3E                                |     |

| 6.6.2.Cray T3D                                |     |

| 6.6.3.Digital Alphaserver 8400                               | 222 |

|--------------------------------------------------------------|-----|

| 6.6.4.IBM SP2                                                |     |

| 6.6.5. Silicon Graphics Origin 2000 (karnak3)                |     |

| 6.6.6.Hitachi SR2201                                         | 228 |

| 6.7. RESULTADOS DEL MODELO COLECTIVO COMO MODELO DE PREDICC  | IÓN |

| DEL TIEMPO DE CÓMPUTO                                        | 230 |

| 6.7.1.La Transformada rápida de Fourier                      | 230 |

| 6.7.2.El Algoritmo de ordenación por Muestreo Regular (PSRS) | 231 |

| 6.8.El coste de las funciones de división                    | 232 |

| 6.8.1.Cray T3E                                               | 233 |

| 6.8.2.Cray T3D                                               |     |

| 6.8.3. Silicon Graphics Origin 2000 (karnak3)                | 239 |

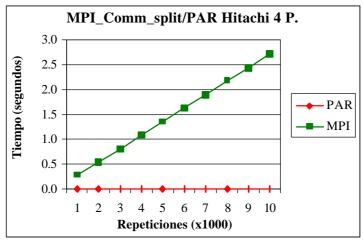

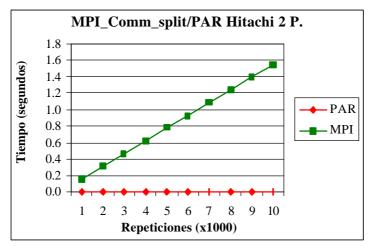

| 6.8.4.Hitachi SR2201                                         |     |

| Conclusiones y Trabajos Futuros                              | 245 |

| Apéndices                                                    | 247 |

| Bibliografías                                                | 253 |

# ÍNDICE DE FIGURAS

| Figura 1.1 Red de estaciones de trabajo                              | . 14 |

|----------------------------------------------------------------------|------|

| Figura 1.2 Estructura de un nodo de la SGI Origin 2000               |      |

| Figura 1.3 Esquema interno de la Digital Alphaserver 8400            | . 18 |

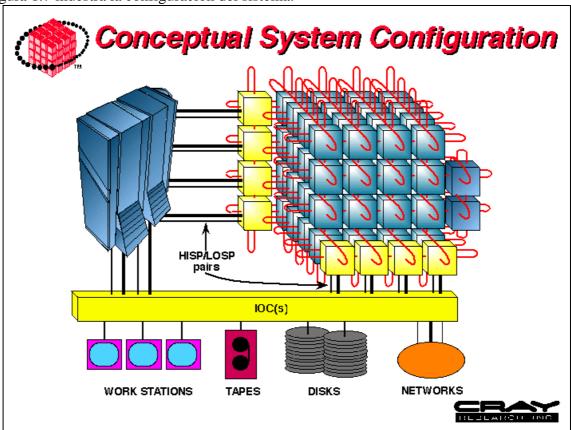

| Figura 1.4 Esquema interno del Cray T3E                              | . 19 |

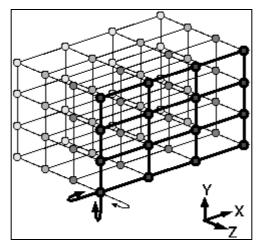

| Figura 1.5 Estructura toroidal del Cray T3E                          | . 20 |

| Figura 1.6 Instalación del Cray T3D en el EPCC                       | 21   |

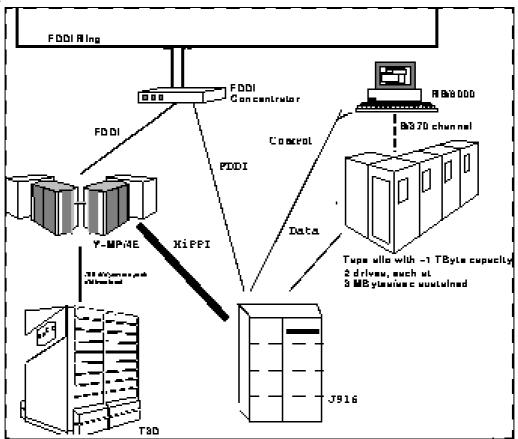

| Figura 1.7 Estructura del Cray T3D                                   | . 22 |

|                                                                      |      |

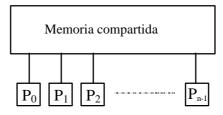

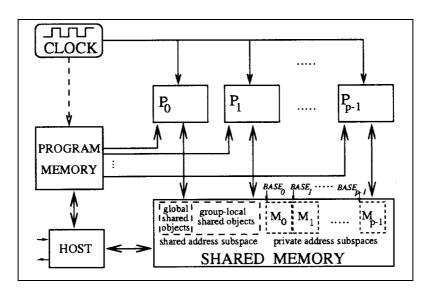

| Figura 2.1 El modelo PRAM                                            | . 25 |

| Figura 2.2 Memoria Compartida CREW de acceso constante               | . 26 |

| Figura 2.3 Bucle secuencial con una sentencia for all                | . 27 |

| Figura 2.4 Sentencias spawn y for all                                | . 28 |

| Figura 2.5 La pareja (Map, F) define una política de asignación de   |      |

| procesadores                                                         | . 29 |

| Figura 2.6 Ejemplo con bucles for all anidados                       | . 30 |

| Figura 2.7 Ejemplo de ejecución del compilador de La Laguna          | . 30 |

| Figura 2.8 Ejemplo rbatcher.ll                                       |      |

| Figura 2.9 Ejecución con el intérprete PRAM                          | . 32 |

| Figura 2.10 Arquitectura de la máquina objeto del compilador de ll . | . 33 |

| Figura 2.11 La traducción de sentencias paralelas anidadas           | 34   |

| Figura 2.12 La implementación de la política cíclica de distribución | de   |

| procesadores                                                         | 35   |

| Figura 2.13 Replicación de la memoria compartida en PVM              | . 36 |

| Figura 2.14 Declaraciones                                            |      |

| Figura 2.15 Resultado de la ejecución de la suma de prefijos         | . 37 |

| Figura 2.16 Suma de prefijos                                         | . 37 |

| Figura 2.17 Procedimiento sort y programa principal                  | . 39 |

| Figura 2.18 Procedimiento para la partición del vector               | 40   |

| Figura 2.19 Sentencia de Asignación de Procesadores Ponderada        | 41   |

| Figura 2.20 Sentencia parallel con control de asignación de          |      |

| procesadores                                                         | 41   |

| Figura 2.21 Sort con asignación ponderada de procesadores            | 41   |

| Figura 2.22 Definiendo una política de asignación                    | 42   |

| Figura 2.23 Distribuyendo los procesadores explícitamente            | 42   |

| F | Figura 2.24 ¿Puede ser la aceleración mayor que el número de              |

|---|---------------------------------------------------------------------------|

| r | procesadores?                                                             |

|   | Figura 2.25 Superlinealidad: Observe el contador de tiempos junto a la    |

|   | etiqueta T                                                                |

|   | Figura 2.26 Ejecución de COPYTOPS en una PRAM con 4                       |

|   | procesadores                                                              |

| - | Figura 2.27                                                               |

| - | 15d1d 2.27                                                                |

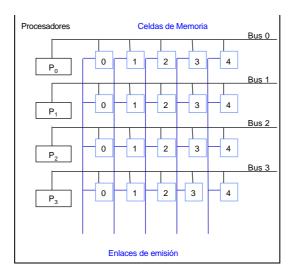

| F | Figura 3.1 Implementación de una PRAM54                                   |

| F | Figura 3.2 Arquitectura de la SB-PRAM55                                   |

|   | Figura 3.3 Red Mariposa de 4 etapas                                       |

|   | Figura 3.4 Topología de la red de la 4-SB-PRAM 57                         |

|   | Figura 3.5 Particionado de la red                                         |

|   | Figura 3.6 Utilización de los paquetes fantasma en los nodos de la red 59 |

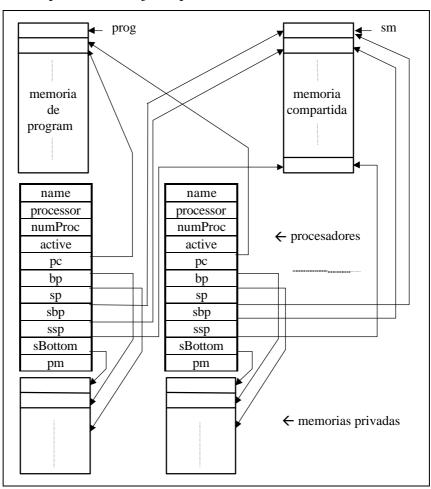

|   | Figura 3.7 Estructura de la SB-PRAM desde el punto de vista del pro-      |

|   | gramador 60                                                               |

|   | Figura 3.8 Un primer programa simple en Fork95                            |

|   | Figura 3.9 La ejecución del programa de la Figura 3.8                     |

|   | Figura 3.10 Un bucle de paralelismo de datos para calcular los cuadra-    |

|   | los de N números                                                          |

|   | Figura 3.11 Resultado de la ejecución del programa de la Figura 3.1064    |

|   | Figura 3.12 Una implementación simple del acceso a una sección            |

|   | erítica                                                                   |

|   | Figura 3.13 El programa de la Figura 3.12 ejecutado por 4                 |

|   | procesadores                                                              |

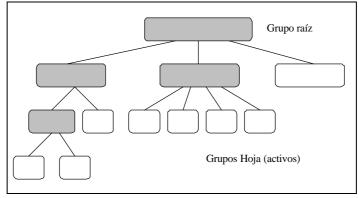

|   | Figura 3.14 La jerarquía de grupos de Fork95                              |

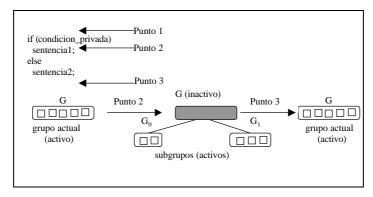

|   | Figura 3.15 La división de los grupos en modo síncrono con una senten-    |

|   | tia condicional con condición privada                                     |

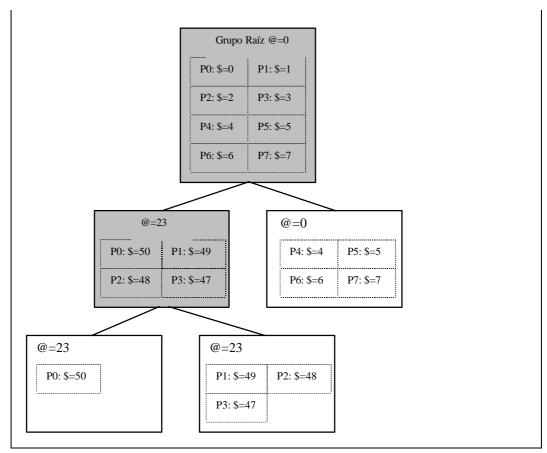

|   | Figura 3.16 Un grupo inicial de procesadores se divide varias veces 70    |

|   | Figura 3.17 Ejecución del programa de la Figura 3.16                      |

|   | Figura 3.18 La jerarquía de grupos correspondiente a la ejecución del     |

|   | programa de la Figura 3.16                                                |

|   |                                                                           |

|   | Figura 3.19 El código entre las líneas 9 y 15 es síncrono                 |

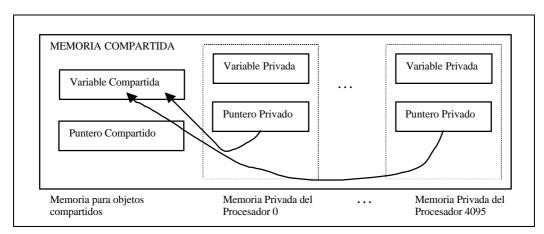

|   | Figura 3.20 Diferentes punteros privados apuntando a la misma variable    |

|   | compartida                                                                |

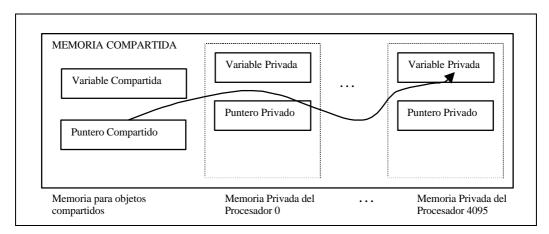

| 1 | Figura 3.21 Una variable privada accesible a todos los procesadores a     |

|   |                                                                           |

|       | s de un puntero compartido                                      |       |

|-------|-----------------------------------------------------------------|-------|

|       | ra 3.22 La suma de prefijos en Fork95                           |       |

| Figur | ra 3.23 Ejecución del programa de la Figura 3.22                | 78    |

| Figur | ra 3.24 El Quicksort en Fork95                                  | 79    |

| Figu  | ra 3.25 El programa principal para el Quicksort de la Fi        | gura  |

| 3.26  |                                                                 | 80    |

| Figur | ra 3.26 Otra implementación del Quicksort en fork95             | 81    |

| _     | ra 3.27 El mergesort en Fork95                                  |       |

|       | ra 3.28 La función merge                                        |       |

| Figu  | ra 3.29 Resultado de la ejecución del mergesort con 5           |       |

| _     | esadores                                                        | 83    |

| Figur | ra 3.30 La Transformada rápida de Fourier en Fork95             | 84    |

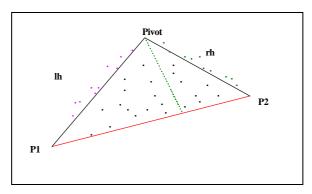

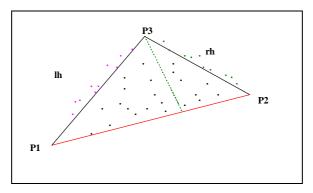

|       | ra 3.31 Cálculo de la envoltura convexa de una nube de punto    |       |

| _     | ra 3.32 La Quickhull en Fork95                                  |       |

| г.    | 445                                                             | 00    |

| _     | ra 4.1 El coste de las funciones de división                    |       |

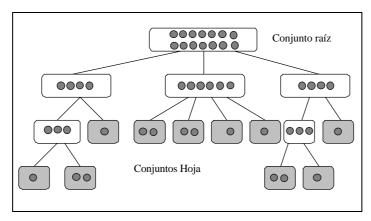

|       | ra 4.2 La estructura jerárquica de los procesadores             |       |

|       | ra 4.3 Una función de división en La Laguna C                   |       |

|       | ra 4.4 Una función de división                                  |       |

| _     | ra 4.5 Profundidad de activación                                |       |

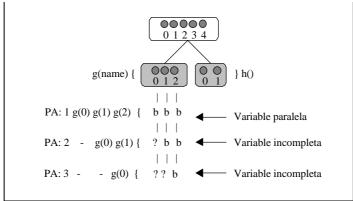

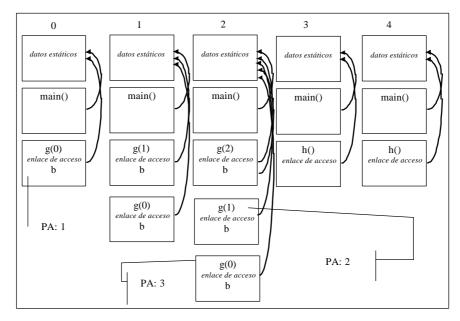

|       | ra 4.6 Una variable incompleta                                  |       |

|       | ra 4.7 Variables paralelas y no paralelas en el momento de la e |       |

|       | de la línea 4 del programa de la Figura 4.6                     |       |

| _     | ra 4.8 No todas las instancias de b definen una variable parale |       |

| _     | ra 4.9 Las activaciones de la función g() de la Figura 4.8      |       |

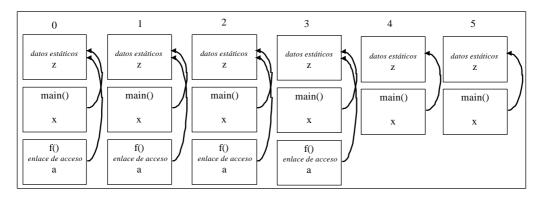

| Figur | ra 4.10 La pila de ejecución para el programa de la Figura 4.8  | 98    |

|       | ra 4.11 Variables comunes y no comunes                          |       |

| Figur | ra 4.12 Variables privadas y comunes                            | . 100 |

| Figur | ra 4.13 Variables resultado                                     | . 100 |

| Figur | ra 4.14 Error en la llamada a una operación colectiva           | . 101 |

| Figu  | ra 4.15 Una operación colectiva común                           | . 102 |

| Figu  | ra 4.16 Una operación colectiva no común                        | . 102 |

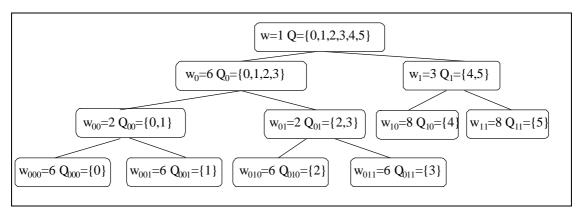

|       | ra 4.17 Un árbol de pesos                                       |       |

|       | ra 4.18 Una jerarquía de dimensiones para un hipercubo          |       |

| binaı | rio de dimensión 2                                              | . 107 |

|       | ra 4.19 Una jerarquía de dimensiones para un hipercubo          |       |

| ternario de dimensión 2 1                                       | 07   |

|-----------------------------------------------------------------|------|

| Figura 4.20 Una jerarquía de dimensiones para un hipercubo o    | di-  |

| námico de dimensión 3 1                                         |      |

| Figura 4.21 Esquema general de un algoritmo divide y vencerá    |      |

| secuencial 1                                                    |      |

| Figura 4.22 Esquema general de un algoritmo divide y vencerá    |      |

|                                                                 |      |

| paralelo                                                        | lige |

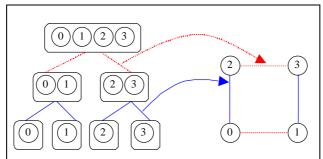

| un socio en conjunto complementario1                            |      |

| Figura 4.24 Los dos grupos se escinden de nuevo en otros dos 1  |      |

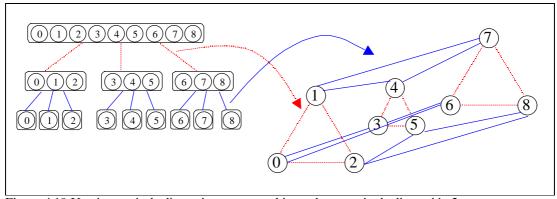

| Figura 4.25 Expansión de una función de división parallel       |      |

| binaria1                                                        | 11   |

| Figura 4.26 Un algoritmo divide y vencerás paralelo con altern  | ıa-  |

| tiva secuencial 1                                               |      |

| Figura 4.27 La Transformada rápida de Fourier en llc 1          | 13   |

| Figura 4.28 La fase de división 1                               | 13   |

| Figura 4.29 La fase de combinación1                             | 14   |

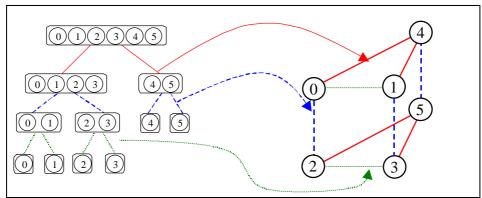

| Figura 4.30 Quickhull en llc1                                   | 14   |

| Figura 4.31 Cálculo de la envoltura convexa de una nube de pu   | ın-  |

| tos1                                                            | 15   |

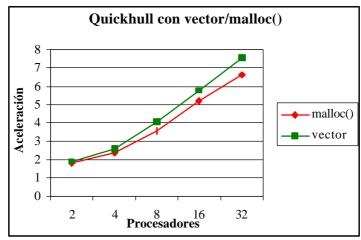

| Figura 4.32 Quickhull con vector/malloc Cray T3D. Tamaño: 11    |      |

| puntos                                                          | 16   |

| Figura 4.33 El Quicksort en llc usando la función de división p | ar   |

| 117                                                             |      |

| Figura 4.34 El Quicksort en llc usando virtualización de        |      |

| procesadores 1                                                  |      |

| Figura 4.35 Búsqueda de KEY en un array desordenado 1           |      |

| Figura 4.36 El procedimiento find 1                             |      |

| Figura 4.37 El Quicksort en llc usando el procedimiento find 1  | .19  |

| Figura 4.38 El Quicksort utilizando la función de división      |      |

| weightedparvirtual 1                                            |      |

| Figura 4.39 El Quickhull usando weightedpar 1                   |      |

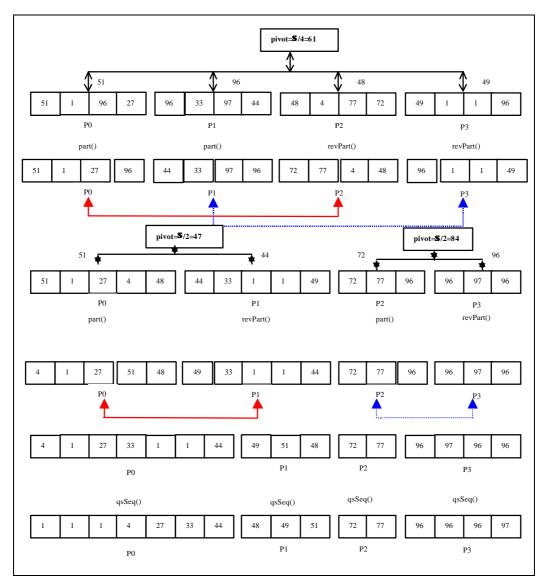

| Figura 4.40 El Quicksort Distribuido 1                          |      |

| Figura 4.41 La función revPart()                                |      |

| Figura 4.42 Una traza del Quicksort Distribuido 1               |      |

| Figura 4.43 Quickhull Distribuida1                              | .26  |

|                                                                 |      |

|              | ra 4.44 Equilibrado de carga por intercambio de datos en e    |     |

|--------------|---------------------------------------------------------------|-----|

|              | ksort distribuido                                             |     |

| _            | a 4.45 Equilibrado de carga por asignación de procesadores 1  |     |

|              | ra 4.46 Código MPI para el algoritmo PSRS                     |     |

| _            | ra 4.48 Merge sort utilizando una reducción dinámica 13       |     |

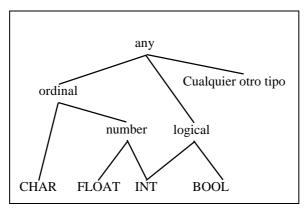

| _            | ra 5.1 La jerarquía de las clases de tipos en NESL14          |     |

| Figur<br>152 | ra 5.2 Implementación de algunas funciones sobre secuenci     | ias |

| Figur        | ra 5.3 Búsqueda de todas las instancias de la palabra p en la | a   |

|              | na s15                                                        |     |

| Figur        | ra 5.4 Hallar todos los primos menores que n1                 | 53  |

| Figur        | ra 5.5 El Quicksort expresado en NESL1                        | 54  |

| Figur        | ra 5.6 El Quicksort en V1                                     | 56  |

| Figura       | a 5.7 Un algoritmo divide y vencerás genérico en Aperitif 1   | 59  |

| Figur        | ra 5.8 El Quicksort en Aperitif10                             | 61  |

| Figur        | ra 6.1 Resultados de la FFT en el Cray T3E del Ciemat 10      | 67  |

| Figur        | ra 6.2 Resultados de la FFT en el Cray T3E del EPCC 10        | 68  |

| Figur        | ra 6.3 Resultados de la FFT en el Cray T3D10                  | 69  |

| Figura       | a 6.4 Resultados de la FFT en la Digital Alphaserver 8400 1   | 70  |

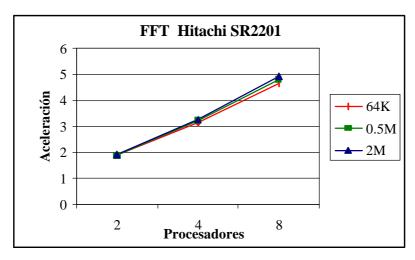

| Figur        | ra 6.5 Resultados de la FFT en la Hitachi SR22011             | 71  |

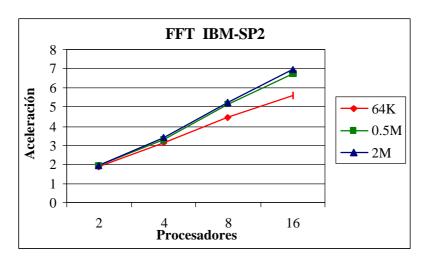

| Figur        | ra 6.6 Resultados de la FFT en la IBM-SP21                    | 72  |

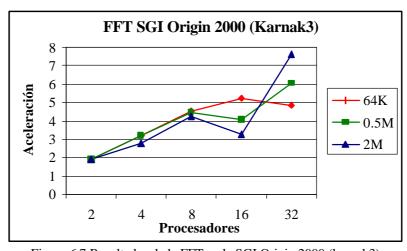

| Figura       | a 6.7 Resultados de la FFT en la SGI Origin 2000 (karnak3) 1  | 73  |

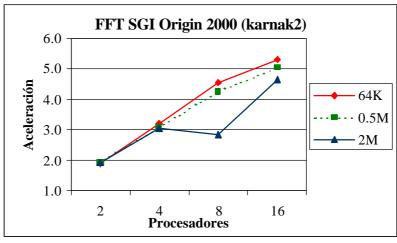

| Figura       | a 6.8 Resultados de la FFT en la SGI Origin 2000 (karnak2) 1  | 74  |

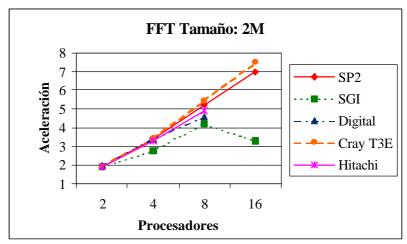

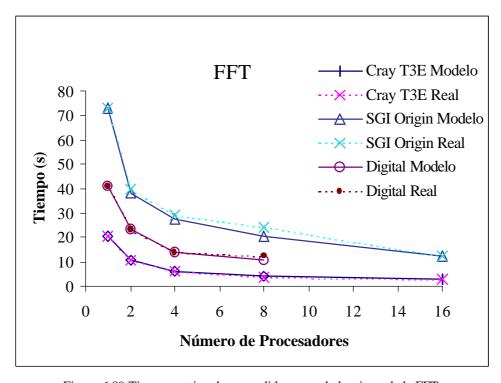

| Figur        | ra 6.9 Resultados de la FFT para tamaño 2M1                   | 75  |

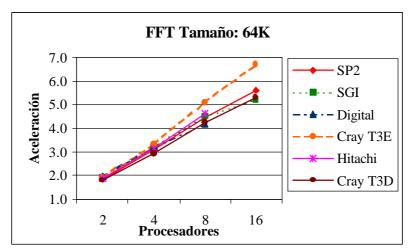

|              | ra 6.10 Resultados de la FFT para tamaño 64K 1                |     |

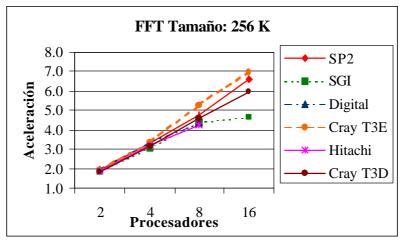

|              | ra 6.11 Resultados de la FFT para tamaño 256K1                | 75  |

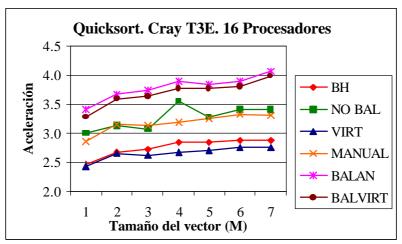

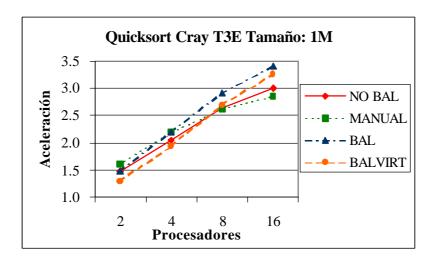

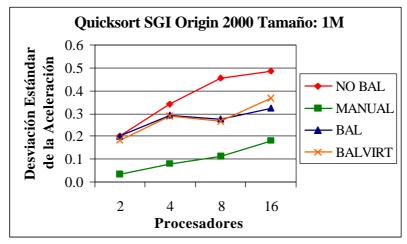

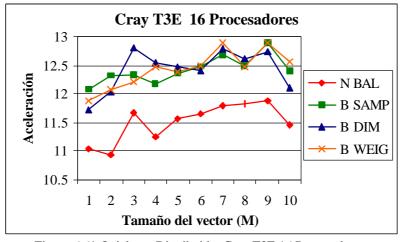

| $\sim$       | ra 6.12 Quicksort. Cray T3E.                                  |     |

| Resul        | tados computacionales para 16 procesadores1                   | 79  |

| Figur        | ra 6.13 Quicksort. Equilibrado de carga. Tamaño del vector    | :   |

|              |                                                               |     |

| Figur        | ra 6.14 Quicksort. Equilibrado de carga. Tamaño del vector    | :   |

|              |                                                               |     |

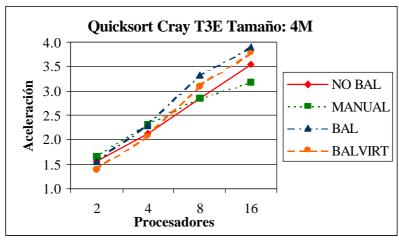

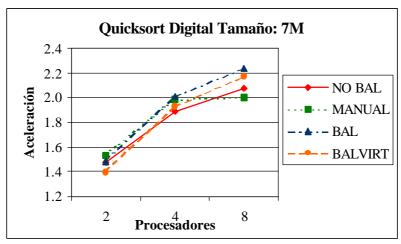

| Figur        | ra 6.15 Quicksort. Equilibrado de carga. Tamaño del vector    | :   |

| 7M180                                                             |

|-------------------------------------------------------------------|

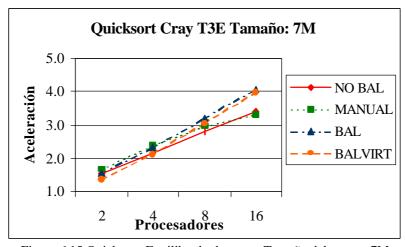

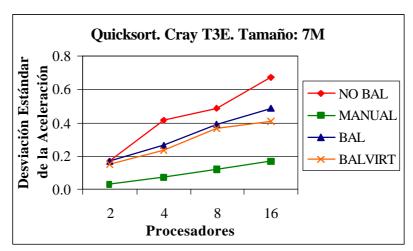

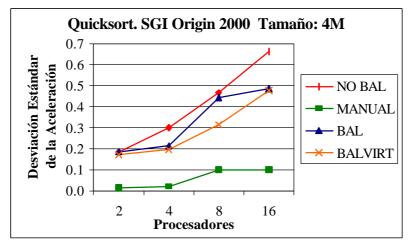

| Figura 6.16 Quicksort. Cray T3E. Desviación Estándar de la Acele- |

| ración para un vector de 7M enteros180                            |

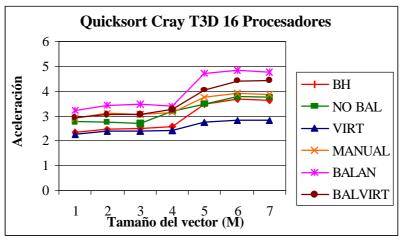

| Figura 6.17 Quicksort. Cray T3D. Resultados computacionales       |

| para 16 procesadores                                              |

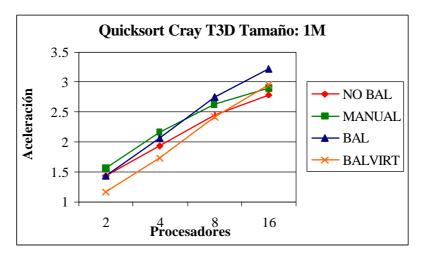

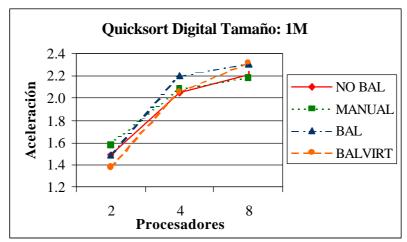

| Figura 6.18 Quicksort. Equilibrado de carga. Tamaño del vector:   |

| 1M                                                                |

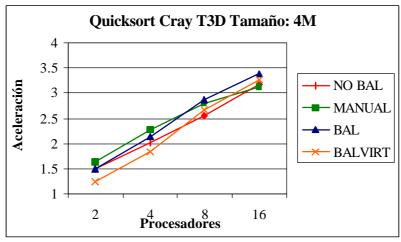

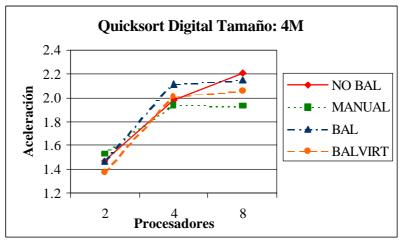

| Figura 6.19 Quicksort. Equilibrado de carga. Tamaño del vector:   |

| 4M182                                                             |

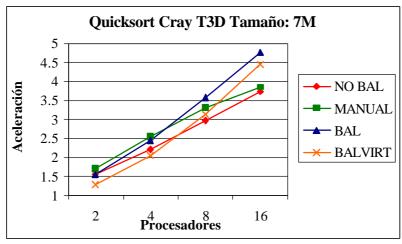

| Figura 6.20 Quicksort. Equilibrado de carga. Tamaño del vector:   |

| 7M183                                                             |

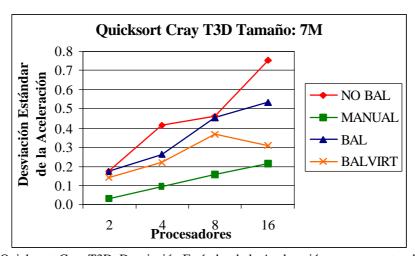

| Figura 6.21 Quicksort. Cray T3D. Desviación Estándar de la Ace-   |

| leración para un vector de 7M enteros183                          |

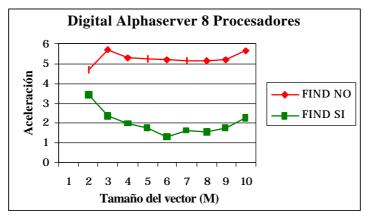

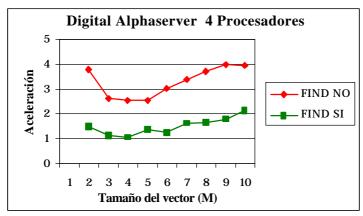

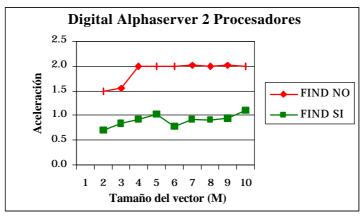

| Figura 6.22 Quicksort. Digital Alphaserver 8400. Resultados       |

| computacionales para 8 procesadores185                            |

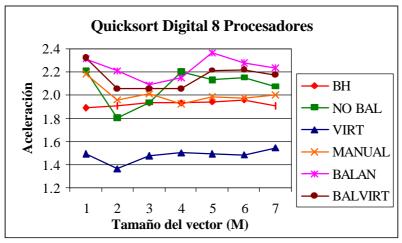

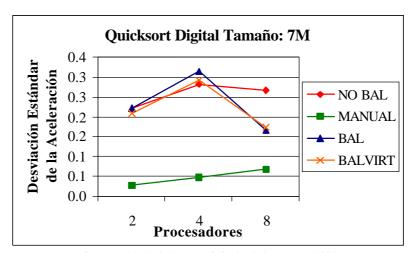

| Figura 6.23 Quicksort. Digital Alphaserver 8400 185               |

| Figura 6.24 Quicksort. Digital Alphaserver 8400 185               |

| Figura 6.25 Quicksort. Digital Alphaserver 8400 186               |

| Figura 6.26 Quicksort. Digital Alphaserver 8400 186               |

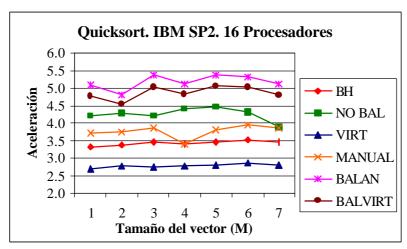

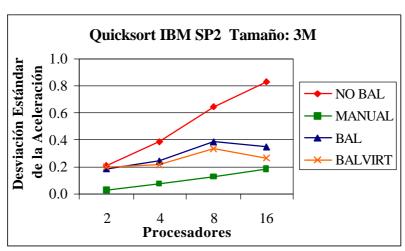

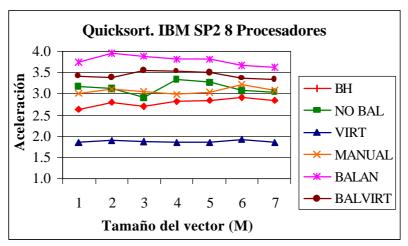

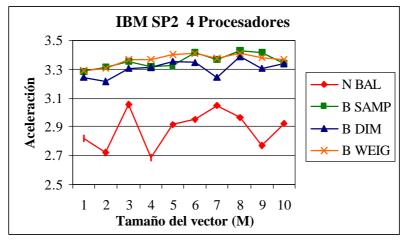

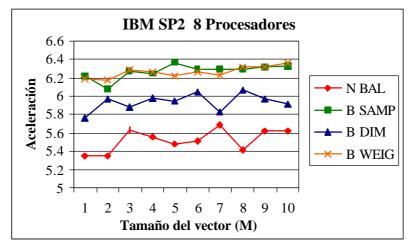

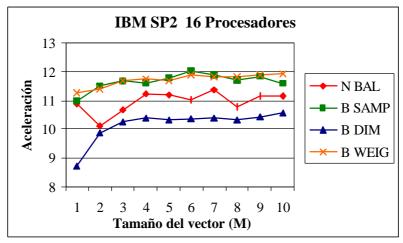

| Figura 6.27 Quicksort. IBM SP2. Resultados computacionales        |

| para 16 procesadores                                              |

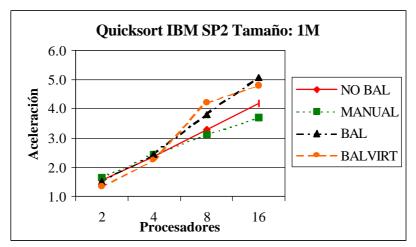

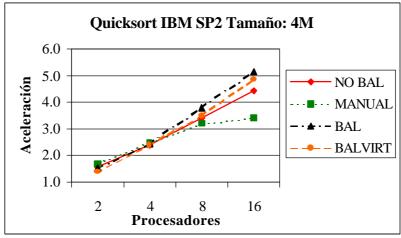

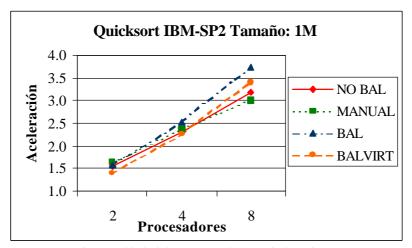

| Figura 6.28 Quicksort. IBM SP2                                    |

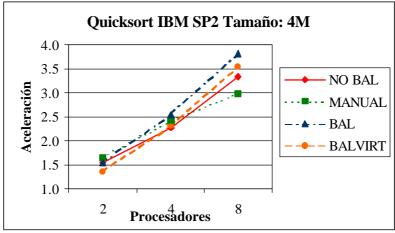

| Figura 6.29 Quicksort. IBM SP2                                    |

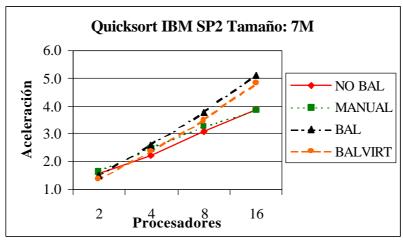

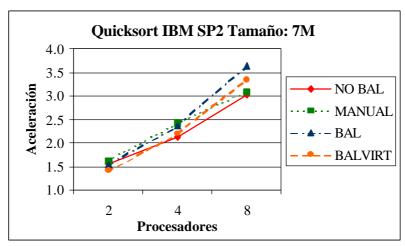

| Figura 6.30 Quicksort. IBM SP2                                    |

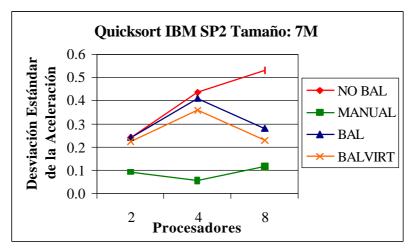

| Figura 6.31 Quicksort. IBM SP2. Desviación Estándar de la Acele-  |

| ración para un vector de 3M enteros189                            |

| Figura 6.32 Quicksort. IBM SP2 (switch antiguo).                  |

| Resultados computacionales para 8 procesadores                    |

| Figura 6.33 Quicksort. IBM SP2 (switch antiguo)                   |

| Figura 6.34 Quicksort. IBM SP2 (switch antiguo)                   |

| Figura 6.35 Quicksort. IBM SP2 (switch antiguo)                   |

| Figura 6.36 Quicksort. IBM SP2 (switch antiguo)                   |

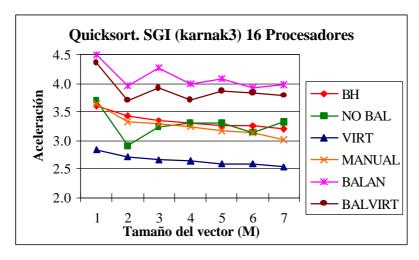

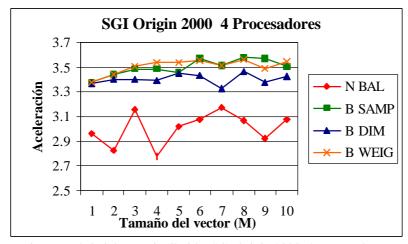

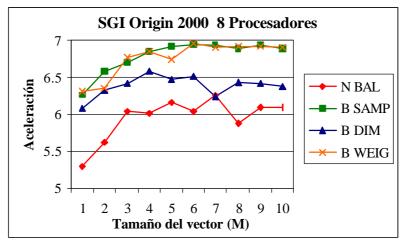

| Figura 6.37 Quicksort. SGI Origin 2000 (karnak3).                 |

| Resultados computacionales para 16 procesadores 194               |

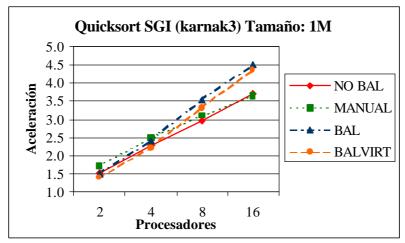

| Figura 6.38 Quicksort. SGI Origin 2000 (karnak3)                  |

| Figura 6.39 Quicksort. SGI Origin 2000 (karnak3)                  |

|                                                                   |

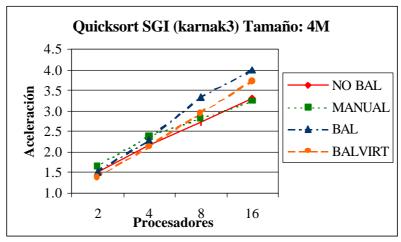

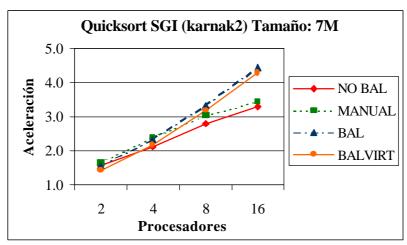

| Figura 6.40 Quicksort. SGI Origin 2000 (karnak3)195              |

|------------------------------------------------------------------|

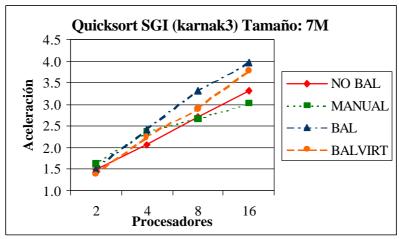

| Figura 6.41 Quicksort. SGI Origin 2000 (karnak3)                 |

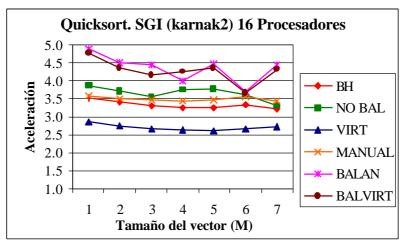

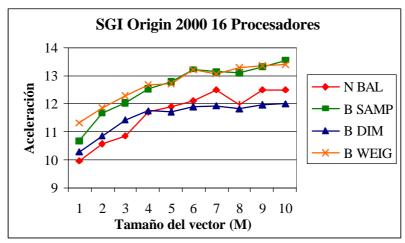

| Figura 6.42 Quicksort. SGI Origin 2000 (karnak2).                |

| Resultados computacionales para 16 procesadores                  |

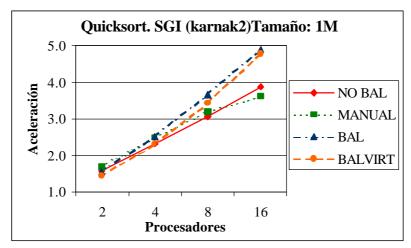

| Figura 6.43 Quicksort. SGI Origin 2000 (karnak2)197              |

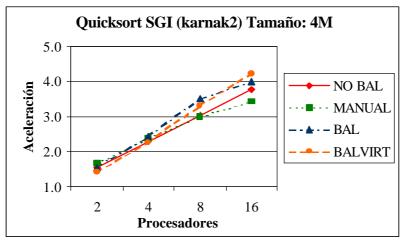

| Figura 6.44 Quicksort. SGI Origin 2000 (karnak2)                 |

| Figura 6.45 Quicksort. SGI Origin 2000 (karnak2)                 |

| Figura 6.46 Quicksort. SGI Origin 2000 (karnak2)                 |

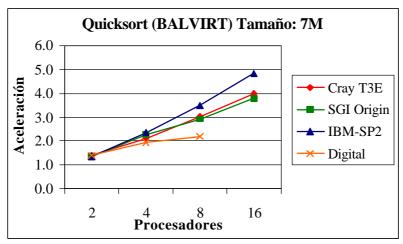

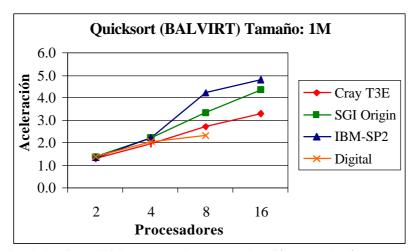

| Figura 6.47 El algoritmo Quicksort con BALVIRT en las diferentes |

| plataformas. Tamaño 7M                                           |

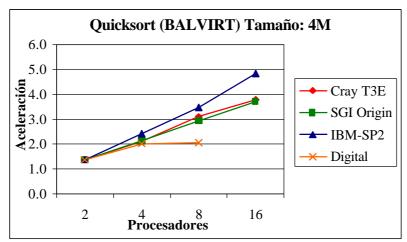

| Figura 6.48 El algoritmo Quicksort con BALVIRT en las diferentes |

| plataformas. Tamaño 4M                                           |

| Figura 6.49 El algoritmo Quicksort con BALVIRT en las diferentes |

| plataformas. Tamaño 1M                                           |

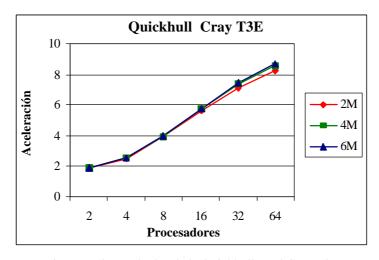

| Figura 6.50 Resultados de la Quickhull en el Cray T3E            |

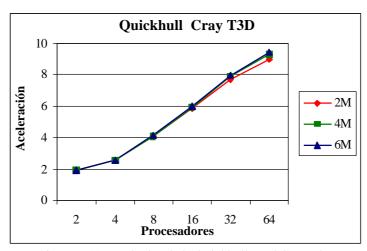

| Figura 6.51 Resultados de la Quickhull en el Cray T3D 202        |

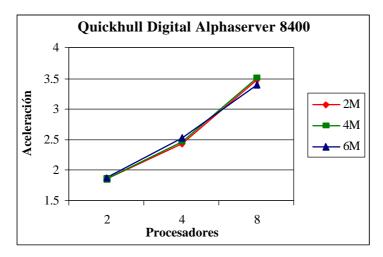

| Figura 6.52 Resultados de la Quickhull en el Digital Alphaserver |

| 8400                                                             |

| Figura 6.53 Resultados de la Quickhull en el Hitachi SR2201 204  |

| Figura 6.54 Resultados de la Quickhull en el IBM SP2             |

| Figura 6.55 Resultados de la Quickhull en el SGI Origin 2000     |

| (karnak3)                                                        |

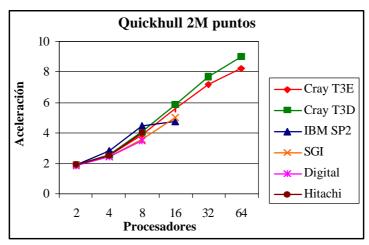

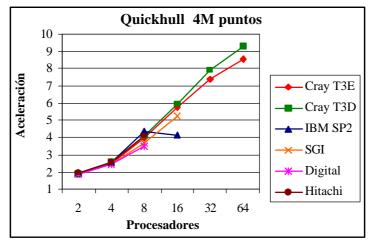

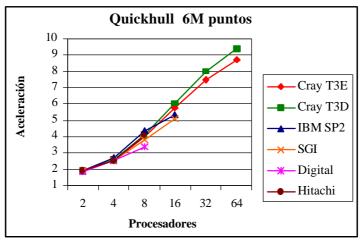

| Figura 6.56 Resultados de la Quickhull en diferentes máquinas    |

| para 2M puntos                                                   |

| Figura 6.57 Resultados de la Quickhull en diferentes máquinas    |

| para 4M puntos                                                   |

| Figura 6.58 Resultados de la Quickhull en diferentes máquinas    |

| para 6M puntos                                                   |

| Figura 6.59 Quicksort Distribuido. Cray T3E 4 Procesadores 210   |

| Figura 6.60 Quicksort Distribuido. Cray T3E 8 Procesadores 210   |

| Figura 6.61 Quicksort Distribuido. Cray T3E 16 Procesadores. 210 |

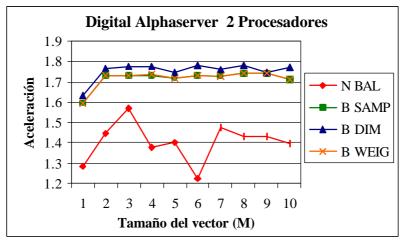

| Figura 6.62 Quicksort Distribuido. Digital Alphaserver 2         |

| Procesadores                                                     |

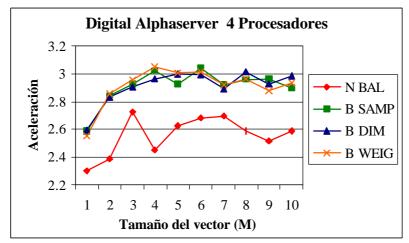

| Figura 6.63 Quicksort Distribuido. Digital Alphaserver 4         |

| Procesadores                                                     |

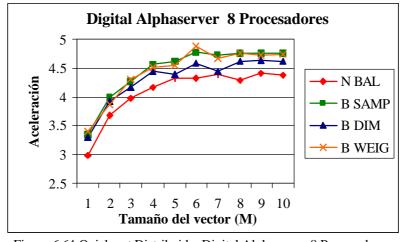

| Figura 6.64 Quicksort Distribuido. Digital Alphaserver 8         |

|                                                                  |

|                                                                  |

| Procesadores212                                                |  |  |  |  |  |

|----------------------------------------------------------------|--|--|--|--|--|

| Figura 6.65 Quicksort Distribuido. IBM SP2 4 Procesadores 214  |  |  |  |  |  |

| Figura 6.66 Quicksort Distribuido. IBM SP2 8 Procesadores 214  |  |  |  |  |  |

| Figura 6.67 Quicksort Distribuido. IBM SP2 16 Procesadores.214 |  |  |  |  |  |

| Figura 6.68 Quicksort Distribuido. SGI Origin 2000 4           |  |  |  |  |  |

| Procesadores                                                   |  |  |  |  |  |

| Figura 6.69 Quicksort Distribuido. SGI Origin 2000 8           |  |  |  |  |  |

| Procesadores                                                   |  |  |  |  |  |

| Figura 6.70 Quicksort Distribuido. SGI Origin 2000 16          |  |  |  |  |  |

| Procesadores                                                   |  |  |  |  |  |

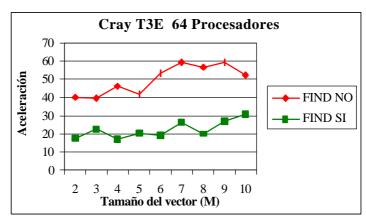

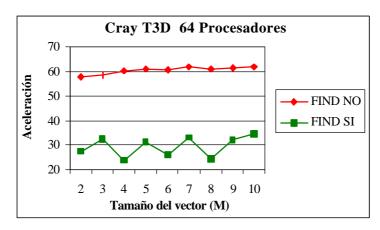

| Figura 6.71 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para el Cray T3E con 64 procesadores                |  |  |  |  |  |

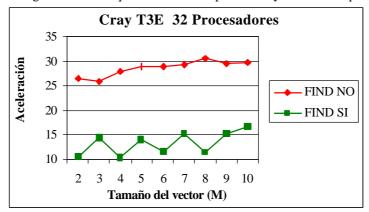

| Figura 6.72 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para el Cray T3E con 32 procesadores                |  |  |  |  |  |

| Figura 6.73 Algoritmo de Búsqueda.                             |  |  |  |  |  |

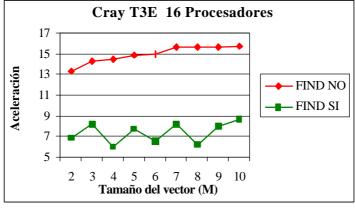

| Resultados para el Cray T3E con 16 procesadores                |  |  |  |  |  |

| Figura 6.74 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para el Cray T3D con 64 procesadores221             |  |  |  |  |  |

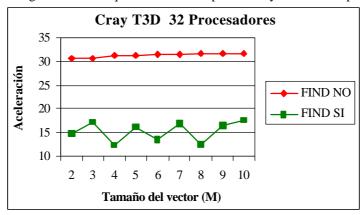

| Figura 6.75 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para el Cray T3D con 32 procesadores221             |  |  |  |  |  |

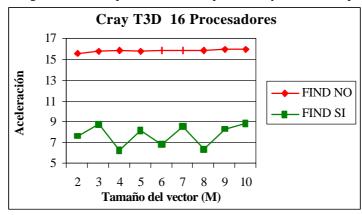

| Figura 6.76 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para el Cray T3D con 16 procesadores                |  |  |  |  |  |

| Figura 6.77 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para el Digital Alphaserver con 8 procesadores 223  |  |  |  |  |  |

| Figura 6.78 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para el Digital Alphaserver con 4 procesadores 223  |  |  |  |  |  |

| Figura 6.79 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para el Digital Alphaserver con 2 procesadores 223  |  |  |  |  |  |

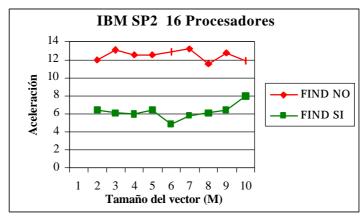

| Figura 6.80 Algoritmo de Búsqueda.                             |  |  |  |  |  |

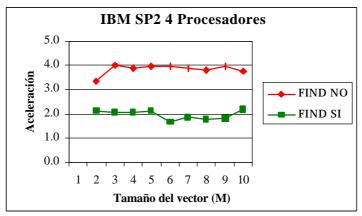

| Resultados para la IBM SP2 con 16 procesadores 225             |  |  |  |  |  |

| Figura 6.81 Algoritmo de Búsqueda.                             |  |  |  |  |  |

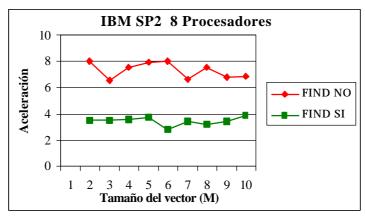

| Resultados para la IBM SP2 con 8 procesadores                  |  |  |  |  |  |

| Figura 6.82 Algoritmo de Búsqueda.                             |  |  |  |  |  |

| Resultados para la IBM SP2 con 4 procesadores                  |  |  |  |  |  |

| Figura 6.83 Algoritmo de Búsqueda.                             |  |  |  |  |  |

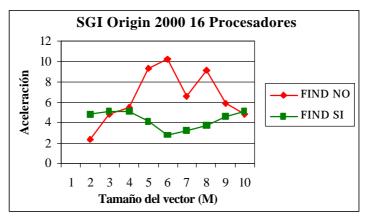

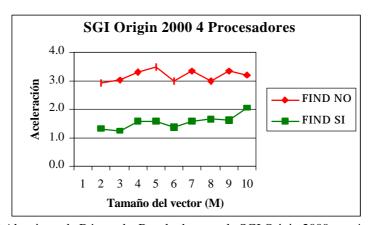

| Resultados para la SGI Origin 2000 con 16 procesadores 227     |  |  |  |  |  |

| <del>-</del>                                                   |  |  |  |  |  |

|                                                                |  |  |  |  |  |

| Figura 6.84 Algoritmo de Búsqueda.                                 |

|--------------------------------------------------------------------|

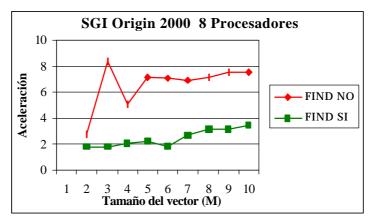

| Resultados para la SGI Origin 2000 con 8 procesadores 227          |

| Figura 6.85 Algoritmo de Búsqueda.                                 |

| Resultados para la SGI Origin 2000 con 4 procesadores 227          |

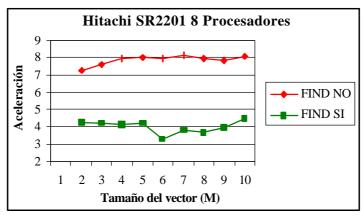

| Figura 6.86 Algoritmo de Búsqueda.                                 |

| Resultados para la Hitachi SR2201 con 8 procesadores 229           |

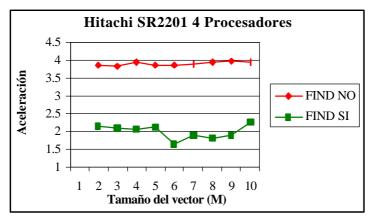

| Figura 6.87 Algoritmo de Búsqueda.                                 |

| Resultados para la Hitachi SR2201 con 4 procesadores 229           |

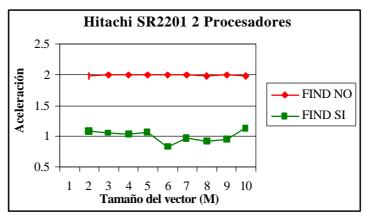

| Figura 6.88 Algoritmo de Búsqueda.                                 |

| Resultados para la Hitachi SR2201 con 2 procesadores 229           |

| Figura 6.89 Tiempos estimados y medidos para el algoritmo de la    |

| FFT                                                                |

| Figura 6.90 Tiempos estimados y medidos para el algoritmo          |

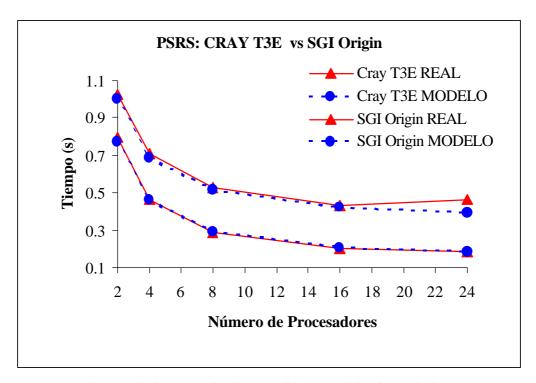

| PSRS231                                                            |

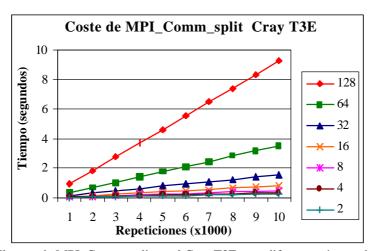

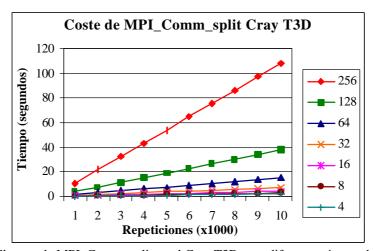

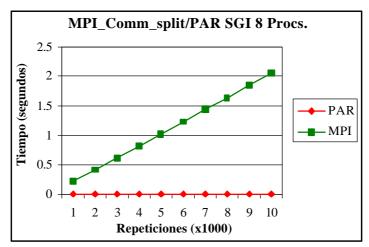

| Figura 6.91 El coste de MPI_Comm_split en el Cray T3E para di-     |

| ferente número de procesadores233                                  |

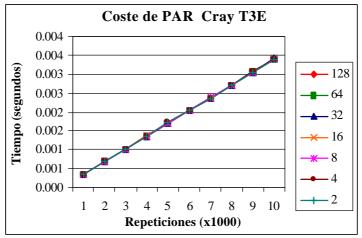

| Figura 6.92 El coste de la función de división PAR en el Cray      |

| T3E234                                                             |

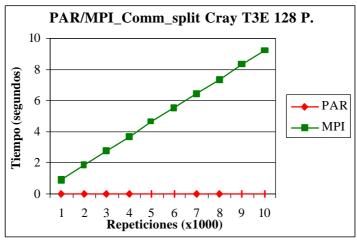

| Figura 6.93 El coste de las funciones de división en el Cray T3E.  |

| 128 Procesadores                                                   |

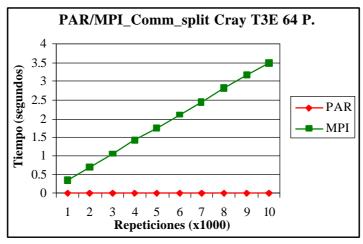

| Figura 6.94 El coste de las funciones de división en el Cray T3E.  |

| 64 Procesadores                                                    |

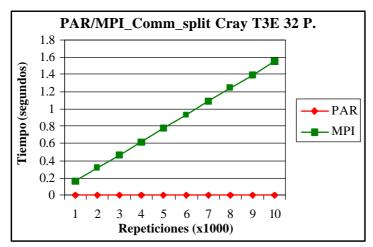

| Figura 6.95 El coste de las funciones de división en el Cray T3E.  |

| 32 Procesadores                                                    |

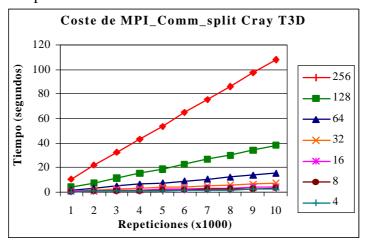

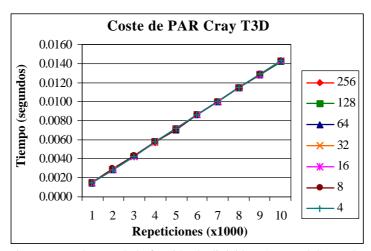

| Figura 6.96 El coste de MPI_Comm_split en el Cray T3D para di-     |

| ferente número de procesadores                                     |

| Figura 6.97 El coste de la función de división PAR en el Cray      |

| T3D237                                                             |

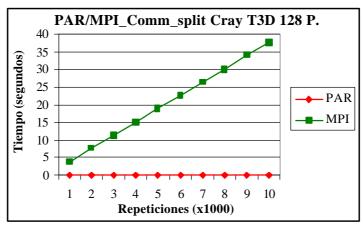

| Figura 6.98 El coste de las funciones de división en el Cray T3D.  |

| 256 Procesadores                                                   |

| Figura 6.99 El coste de las funciones de división en el Cray T3D.  |

| 128 Procesadores                                                   |

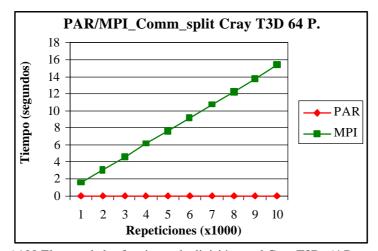

| Figura 6.100 El coste de las funciones de división en el Cray T3D. |

| 64 Procesadores                                                    |

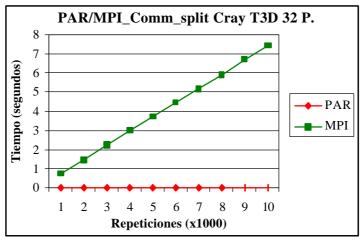

| Figura 6.101 El coste de las funciones de división en el Cray T3D. |

| 32 Procesadores                                                    |

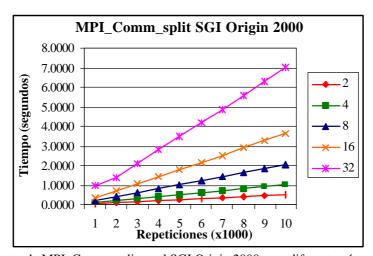

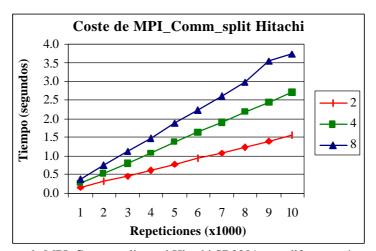

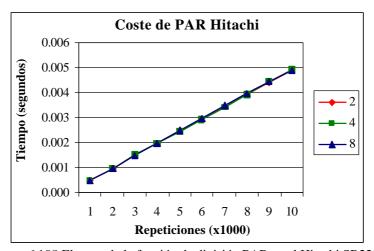

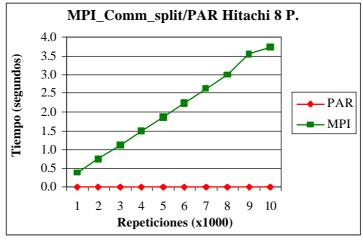

| Figura 6.102 El coste de MPI_Comm_split en el SGI Origin 2000     |

|-------------------------------------------------------------------|

| para diferente número de procesadores239                          |

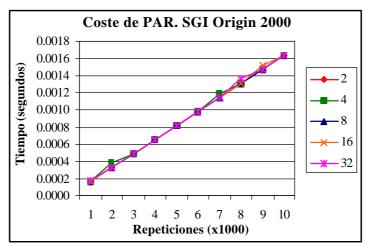

| Figura 6.103 El coste de la función de división PAR en el SGI     |

| Origin 2000240                                                    |

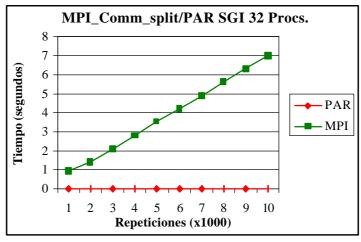

| Figura 6.104 El coste de las funciones de división en el SGI      |

| Origin 2000. 32 Procesadores240                                   |

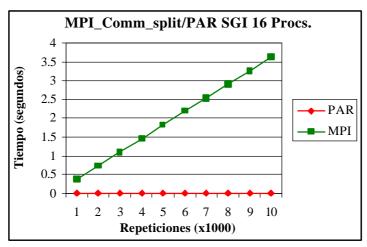

| Figura 6.105 El coste de las funciones de división en el SGI      |